I wrote many posts on different VHDL topics. Many of them deal with quite a complex concept.

Some days ago, I realized that I didn’t write anything “simple” dealing with the basic hardware building block.

I realized that since I received many email and telegram messages asking me to explain them some line of VHDL code. These lines are relative to a simple shift register implementation.

Sometimes what is simple for you, is not for other people!

In this post, I would like to propose three different ways of implementing a shift register in VHDL.

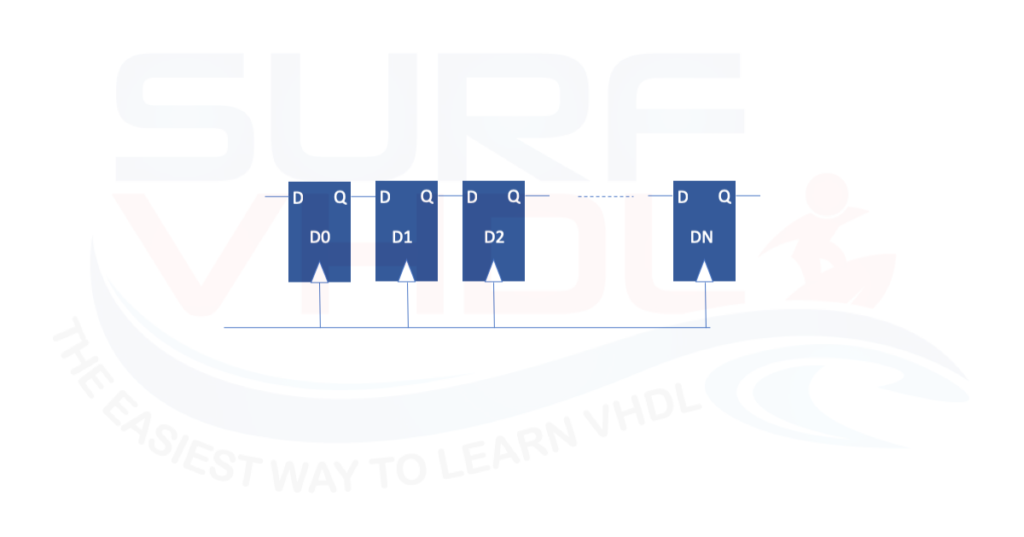

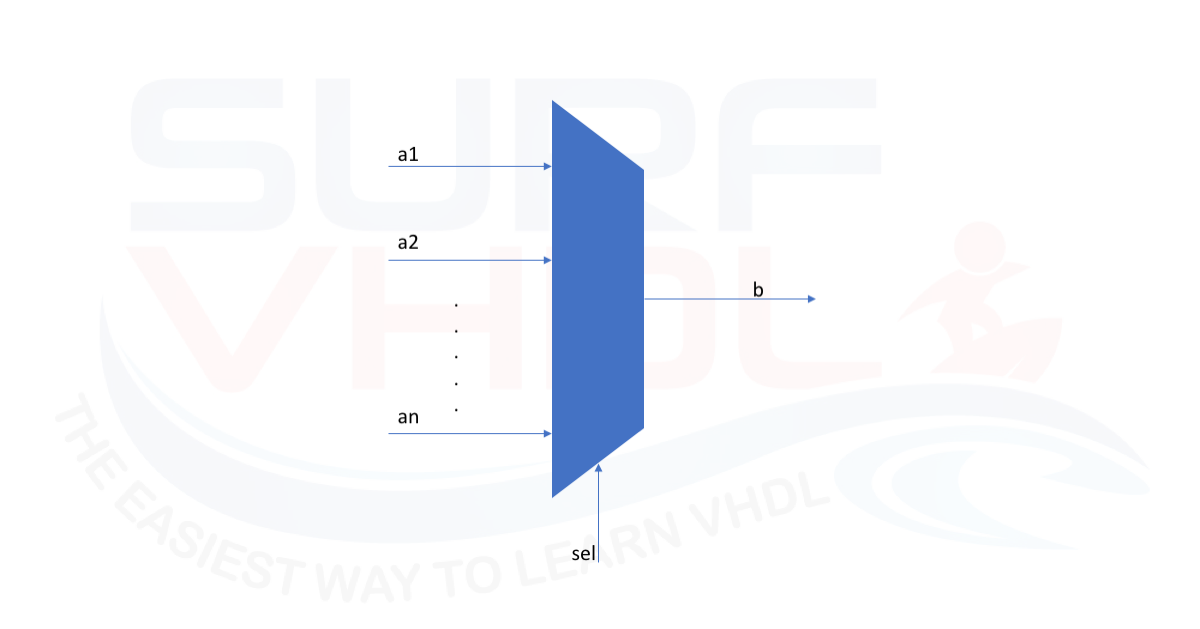

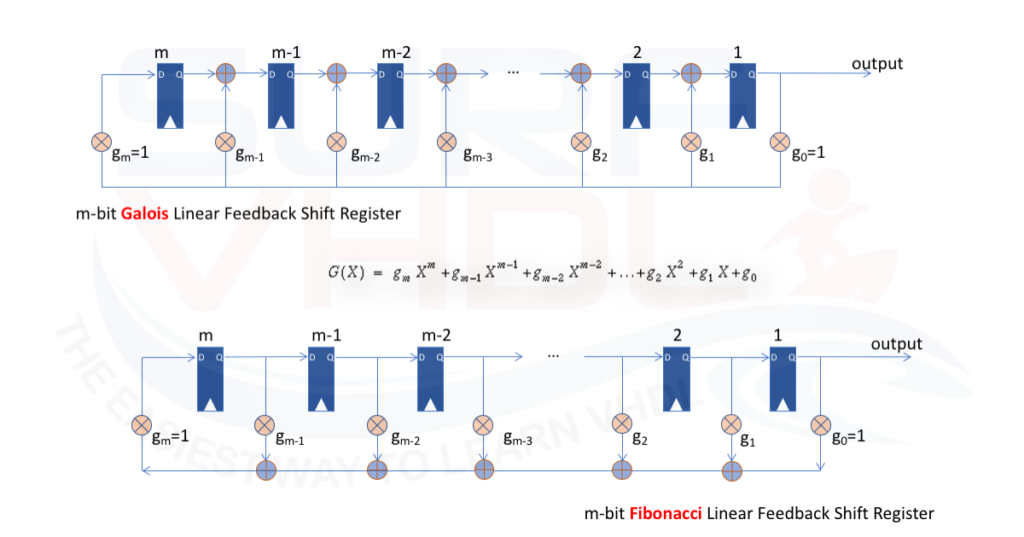

First of all, let’s review what is a shift register. It could be represented with a series of flip flop connected in series, where the output of one flip-flop is the input of the other.

In Figure 1 you can see a visual representation.

As stated before, there are at least three different ways to describe such hardware structure in VHDL. The three descriptions are totally equivalent.