VHDL integer division should be really avoided?

In VHDL there are the math primitive subtraction, addiction, and multiplication that are generally available in the libraries provided by the FPGA or ASIC vendor.

For example, in this post, we saw how to implement a pipelined multiplier. The example shows the use of multiplication and addition primitives.

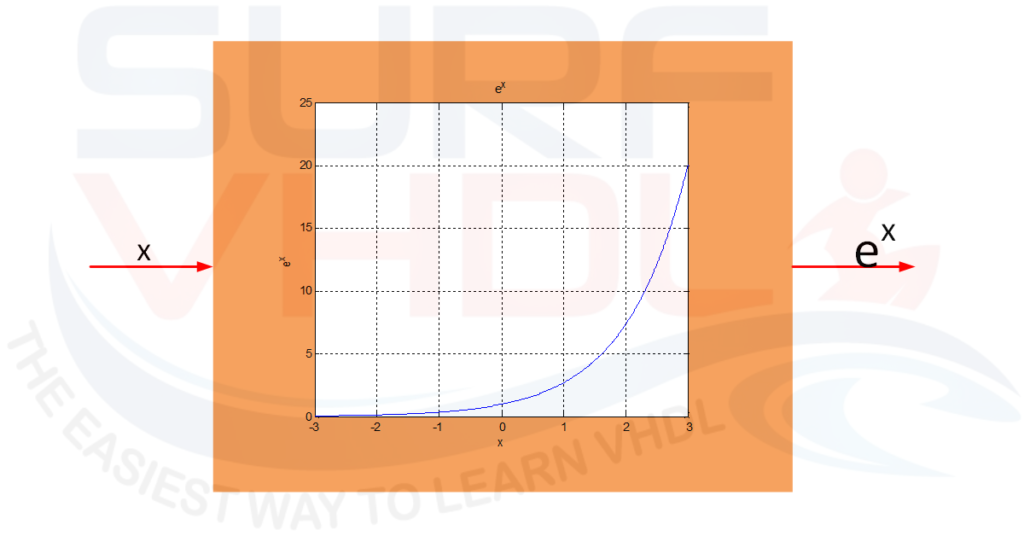

The division is a bit more complex case. Generally, the deployment of the division requires a much more complex logic circuit, and for this reason, we tend to avoid, where possible, the use of the division operator unless there are special cases.

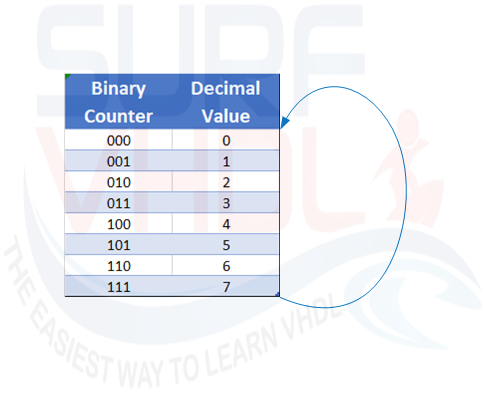

If we have to divide by 2 or power of two, the implementation is simply shifting to the right of the number to divide.

In binary representation, shifting to the right of a position corresponds to a division by two, as in a decimal representation a shifting to the right corresponds to a division by 10.