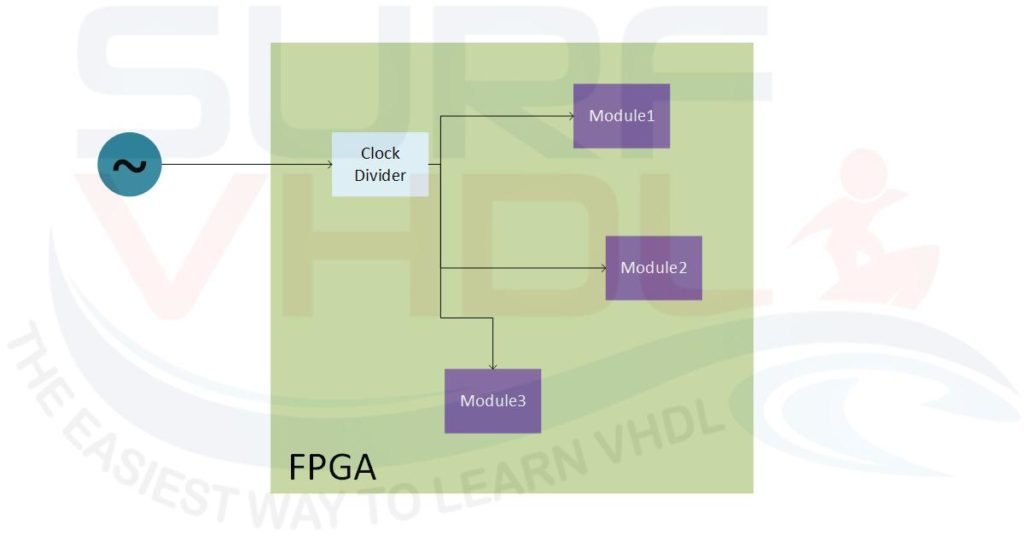

Clock Design Overview

Often, inside our FPGA design, we have the necessity to generate a local clock from the system clock. With system clock, I mean the clock that is coming from an external board oscillator. Many modern FPGAs have the possibility to generate internal clocks, different from the external clocks, using internal PLL hard macro. So you can generate internal FPGA clock as multiple or sub-multiple of the external system clock.

Sometimes the PLL are used to modify the clock phase or to generate different clocks at the same frequency with different phase relationship. For instance, 3 clocks: