Debugging an FIR in FPGA

The VHDL, and other hardware description languages such as Verilog, SistemVerolog and so on, allow us to simulate your digital design in a very accurate way.

If you write a good VHDL code after the simulation you are very confident that your VHDL design will work as it should. When you go to silicon often there are problems and you should debug your VHDL code.

Here you can find some of the common issues you have during the test of VHDL design on FPGA. The modern FPGAs allow the user to enable debug facility inside the silicon using a proprietary debug tool very like an embedded logic state analyzer.

Using Altera Quartus II you can enable the Signal Tap Analyzer or the equivalent using Xilinx Chipscope.

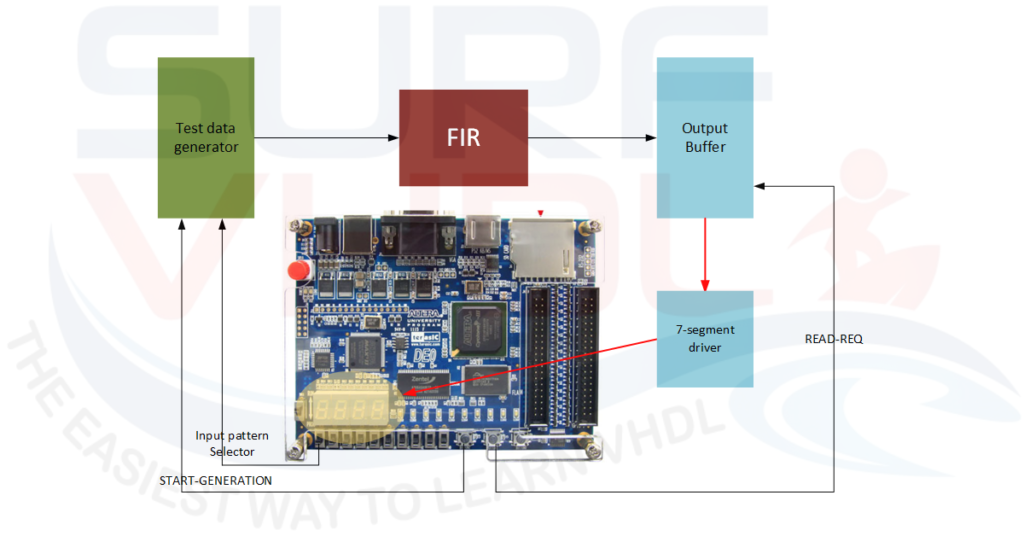

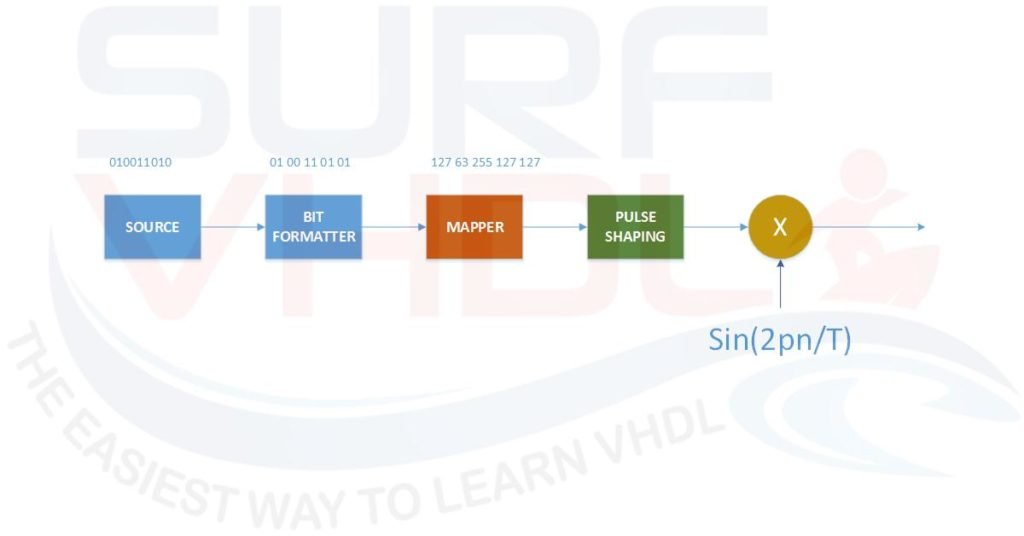

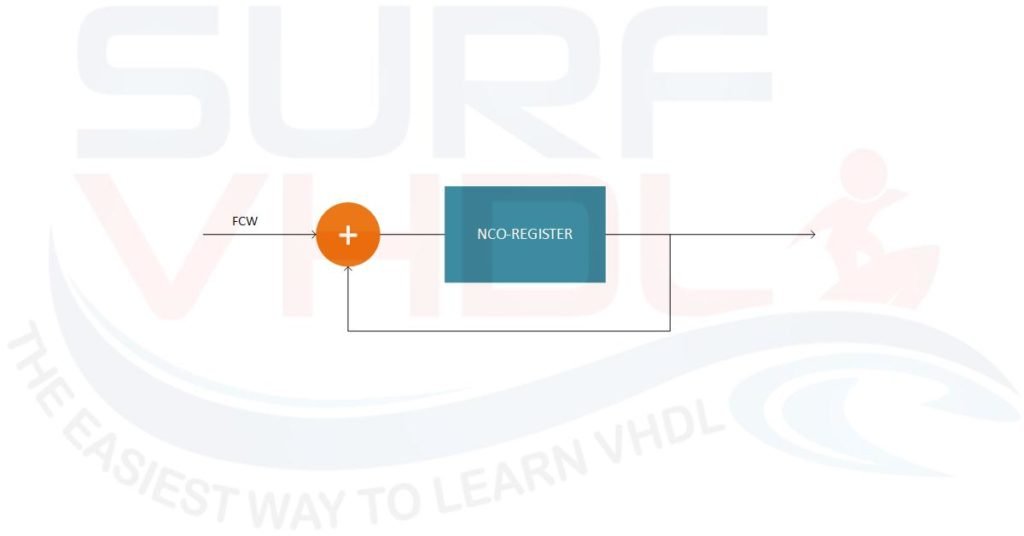

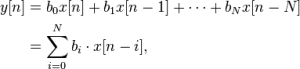

In this post, we are going to see an example of how to debug an FIR using the push button and the seven-segment display of a typical demo board with an FPGA, implementing a complete VHDL test bench that will be implemented in a Terasic DE0 board.

Read More