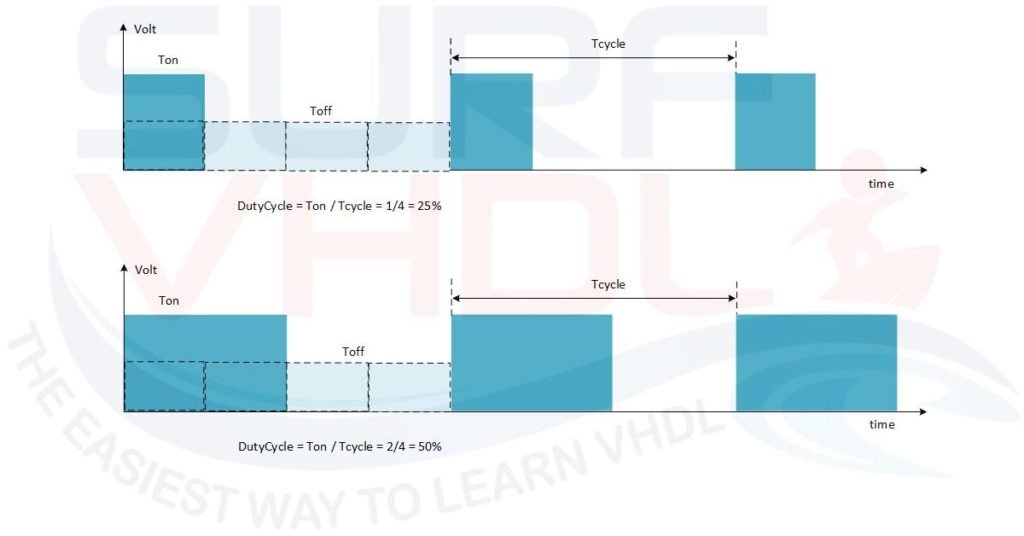

Introduction to PWM

Pulse width modulation (PWM) is a digital technique used for controlling an analog circuit.

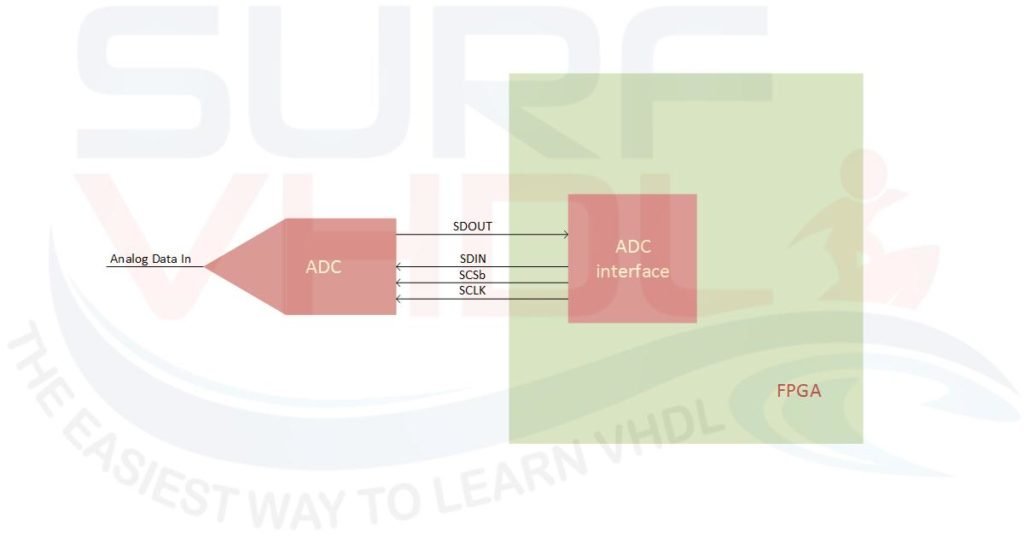

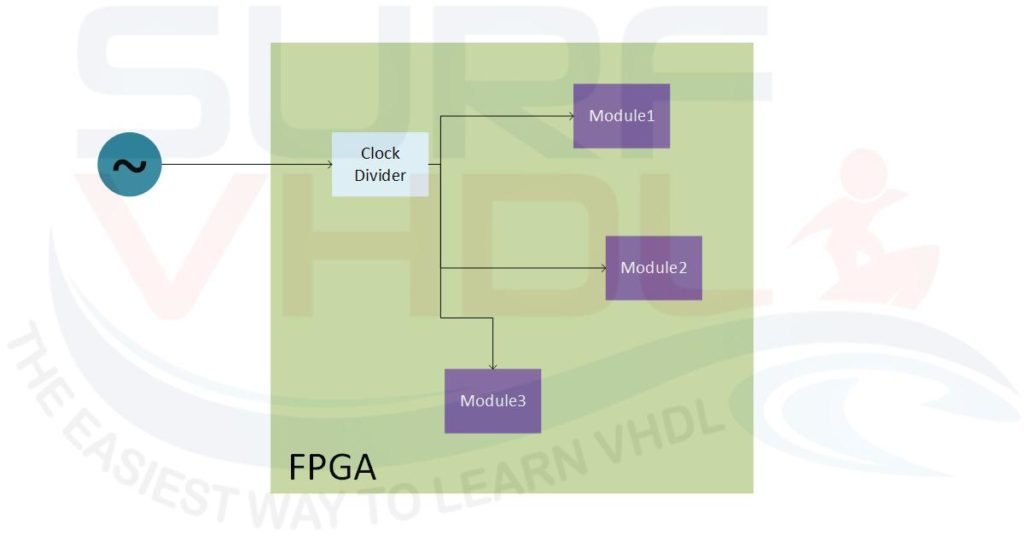

A PWM controller can be implemented either using a microcontroller or an FPGA digital outputs.

The PWM is employed in a wide multiplicity of applications, ranging from measurement and communications to power control, conversion.