Why we need an encoder

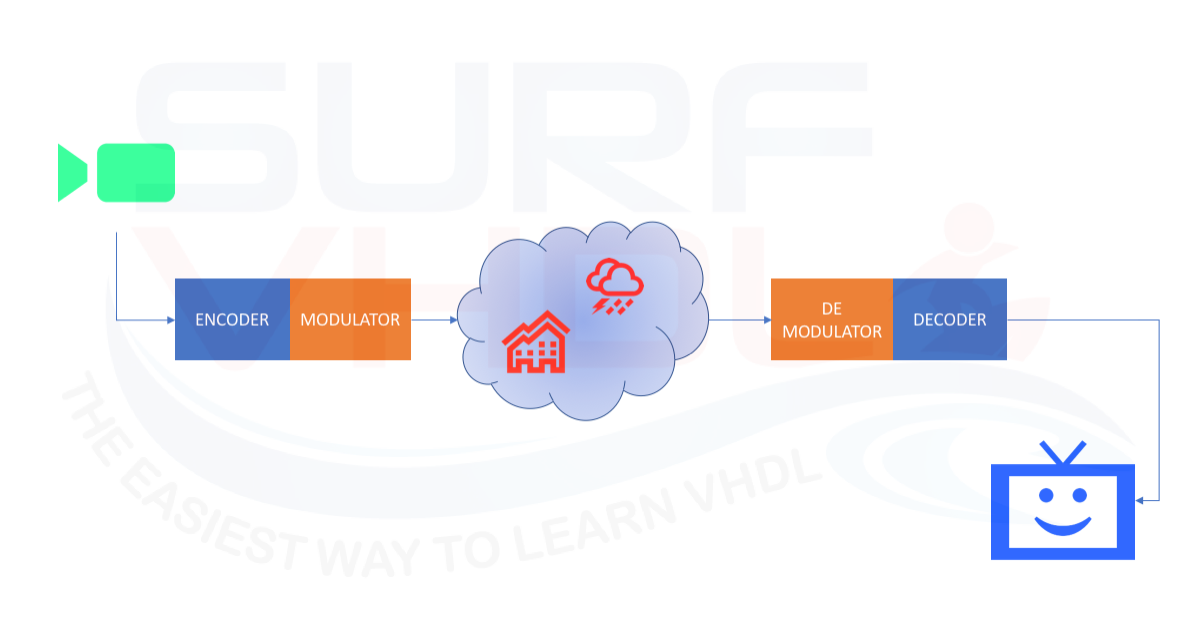

In the communication link, the noise, multipath effect and all the other effects that affect the communication can induce errors on the communication link. In this post, we already addressed the topic introducing the Reed-Solomon encoder.

Here we want to exploit another encoder widely used in communication link: Convolutional Encoder.

After a brief introduction to the Convolutional encoder, we will go to see the thing that interests us the most, I mean the VHDL implementation of a Convolutional Encoder.

Convolutional Encoder Architecture

When we talk about encoders, we can classify the channel coding in two main categories:

BLOCK CODING:

- Cyclic codes

- BCH

- Reed-Solomon

- Product Turbo code

- LDPC

TRELLIS CODING:

- Convolutional coding

- TCM (Trellis Code Modulation)

- Turbo codes (SCCC or PCCC)

- Turbo TCM

In this post, we are going to analyze the architecture of the Convolutional Encoder used in DVB-S standard and its implementation in VHDL.

The convolutional encoder is based on a rate 1/2 mother convolutional code with constraint length K = 7 corresponding to 64 trellis states.

The input serial stream is encoded in two branch X and Y with the following polynomial:

- X output (171 octal)

- Y output (133 octal)

Figure 2 reports the encoder architecture.

VHDL implementation of Convolutional Encoder

Figure 2 shows the classical architecture of a convolutional encoder.

The VHDL implementation is straightforward. Just implement the delay line end the two branches with XOR as below.

library ieee;

use ieee.std_logic_1164.all;

entity conv_encoder is

port (

i_clk : in std_logic;

i_rstb : in std_logic;

i_sync_reset : in std_logic;

i_data_enable : in std_logic;

i_data : in std_logic;

o_data_valid : out std_logic;

o_data_out_x : out std_logic;

o_data_out_y : out std_logic);

end conv_encoder;

architecture rtl of conv_encoder is

constant C_XPOLY : std_logic_vector(5 downto 0) := ("111001"); -- 1 71 oct, first '1' is not computed since is the input

constant C_YPOLY : std_logic_vector(5 downto 0) := ("011011"); -- 1 33 oct, first '1' is not computed since is the input

signal r_delay : std_logic_vector(5 downto 0);

begin

p_encoder : process(i_clk,i_rstb)

variable v_x : std_logic;

variable v_y : std_logic;

begin

if(i_rstb='0') then

o_data_valid <= '0';

o_data_out_x <= '0';

o_data_out_y <= '0';

r_delay <= (others=>'0');

elsif(rising_edge(i_clk)) then

o_data_valid <= i_data_enable;

if(i_sync_reset='1') then

r_delay <= (others=>'0');

elsif(i_data_enable='1') then

r_delay <= i_data&r_delay(r_delay'length-1 downto 1);

end if;

v_x := i_data;

v_y := i_data;

for i in r_delay'length-1 downto 0 loop

if(C_XPOLY(i)='1') then

v_x := v_x xor r_delay(i);

end if;

if(C_YPOLY(i)='1') then

v_y := v_y xor r_delay(i);

end if;

end loop;

o_data_out_x <= v_x;

o_data_out_y <= v_y;

end if;

end process p_encoder;

end rtl;

VHDL Simulation of Convolutional Encoder

In order to verify the VHDL implementation of the convolutional encoder, the best thing is to simulate the VHDL code and compare the encoder output with a reference pattern.

What is the best way to generate a reference I/O pattern?

Matlab or Octave give us the possibility to generate a reference pattern for the convolutional encoder.

Here below an example of Matlab/Octave command used in the generation of the reference matching vector:

clear all;

clc;

NumBit = 1000;

trellis = poly2trellis(7,[171 133]);

dataIn = randi([0 1],NumBit,1);

% Convolutionally encode the data

dataEnc = convenc(dataIn,trellis);

dataEnc = convenc(dataIn,trellis);

fid = fopen("ConvEnc.txt",'wt');

for i = 1 : NumBit

fprintf(fid,'%4d%4d%4d \n',dataIn(i), dataEnc(2*i-1), dataEnc(2*i));

end;

fclose(fid)

In Figure 3, the yellow “error_flag” signal is used to simplify the matching between the output of the Convolutional Encoder VHDL module and the reference Matlab test vector.

The input and output data to the convolutional encoder is read from the reference file and run-time verified during the VHDL simulation.

Layout of Convolutional Encoder

Figure 4 reports the RTL view of the VHDL code presented above.

In the figure is highlighted the XOR function for X and Y branch.

Conclusion

In this post, we have presented the convolutional encoder general architecture. A VHDL example of a Convolutional encoder has been tailored to the general architecture.

The Matlab/Octave script provided can be used to generate reference vector for VHDL matching.

References

[2] https://www.mathworks.com/

[4] https://www.gnu.org/software/octave/

[5] https://en.wikipedia.org/wiki/Convolutional_code

[6] “Channel coding: Convolutional codes” Vahid Meghdadi, University of Limoges

Great ! ! !

Now…. I m waiting for the decoder…

is is very similar to the encoder, just start from the longer branch

Btw, I will write a post to clarify the implementation

design FM demodulator in VHDL. will u pls give me some guidance

Hi,

i am work on SSI absolute encoder binary output. how i write vhdl code. i will try to work on it. please help to me

can you provide the test bench?

send me an email

can you provide the test bench?

can u provide testbench for it?

Please, provide me a testbench for conv code