A process statement is concurrent statement itself

The VHDL process syntax contains:

- sensitivity list

- declarative part

- sequential statement section

The process statement is very similar to the classical programming language. The code inside the process statement is executed sequentially. The process statement is declared in the concurrent section of the architecture, so two different processes are executed concurrently.

The declaration process statement is

process_label : process(sensitivity_list) -- declarative part begin -- sequential statement end process process_label;

The process label is optional, you can avoid using the label. Labeling all process you use, the code will be clear and it will be simple to arrange the simulation environment.

We will address the process statement in the next lessons. Here there is a simple example of the and_or2 entity implemented with a process.

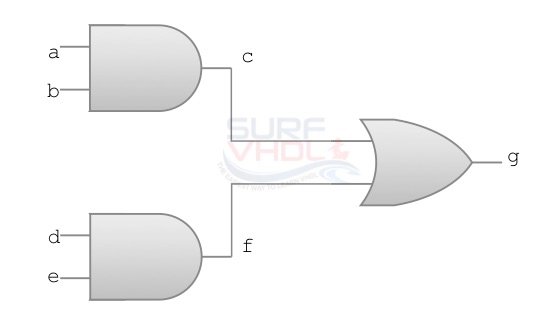

entity and_or is port( a : in std_logic; b : in std_logic; d : in std_logic; e : in std_logic; g : out std_logic); end and_or; architecture and_or_a of and_or is -- declarative part: empty begin process_and_or : process(a,b,d,e) -- declarative part: empty begin g <= (a and b) or (d and e); end process process_and_or; end and_or_a;

The entity declaration is the same as seen in the previous example, in fact the interface versus the external world are identical. In this example, the architecture implementation is different. The architecture declarative section is empty. We don’t need internal signal declaration. The circuit is implemented using a process. In the process sensitivity list are declared all the signal which the process is sensitive to. In fact the process is evaluated any time a transaction is scheduled on the signal a,b,d,e. The process drive the entity output port g. The driver concept is fundamental in VHDL. You shall deeply understand this concept since it is the principal reason of error in the hardware implementation of a VHDL code.