Whenever a signal, in the sensitivity list of a signal assignment statement changes its value, the signal assignment statement is executed.

A signal value is always generated together with the time interval that has to elapse prior to the assignment of that value to the signal: this is known as “scheduling a transaction”.

Therefore, transaction is defined as a value/time pair.

When a signal value is updated, meaning that a transaction is scheduled on that signal, if the new value is different from the previous one, then an event is said to have occurred on the signal.

The following example should clarify the differences between event vs transaction.

architecture behave of event_transaction_example is signal a,b ,c : std_logic; begin a <= '1' after 10 ns, '0' after 12 ns; b <= a after 5 ns; c <= transport a after 5 ns; end behave;

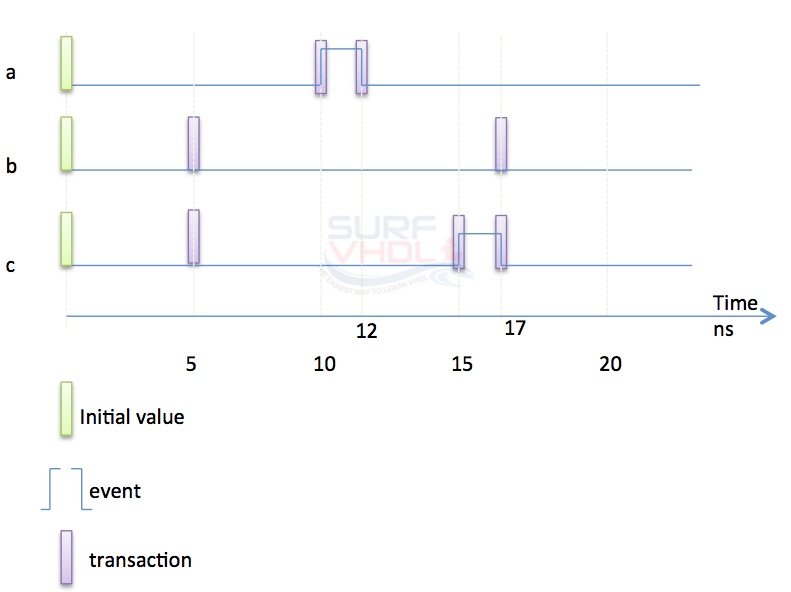

The figure reports the behavior of signal a, b and c.

At time zero a transaction is scheduled on the signals. In fact at time zero all the signal assignment are evaluated in a VHDL design.

The signal a has transaction/event at time 10 ns and transaction/event at time 12 ns.

The signal b has a transaction at time 5 ns and a transaction at time 12 ns.

No event occurs on signal b. The signal a generates a pulse of 2 ns less than the inertial delay of 5 ns

(b <= a after 5 ns). On the signal b only a transaction can be scheduled.

The signal assignment on c is performed as transport delay. In this case c follow the behavior of a.

At 5 ns transaction on b and c are scheduled due to the 5 ns signal assignment.

In this case no new values are generated on the signal so no events occur on these signals.