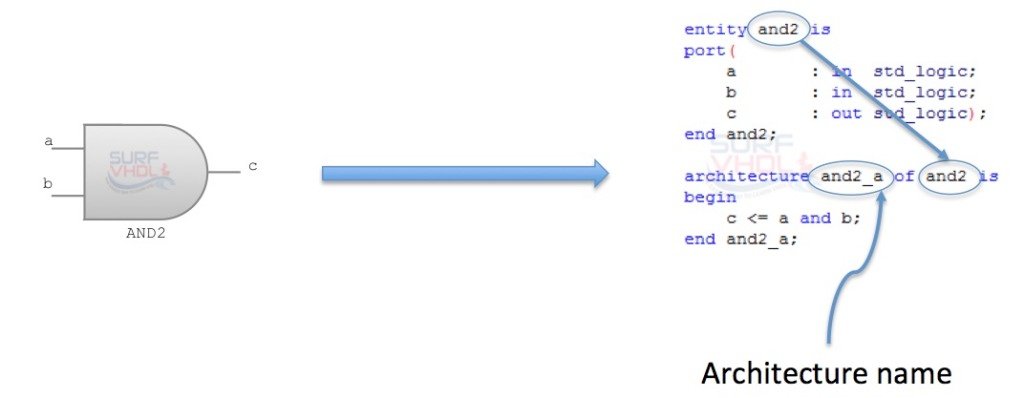

The entity describes the interface of our design. Now, how can we describe the behavior of our entity: what the entity does?

The architecture statement describes the underlying functionality of the entity. Architecture is always related to an entity and describes the behavior of that entity. Remember to follow the Entity/Architecture golden rules in writing your VHDL implementation.

For instance, the entity and2 is described by the architecture named “and2_a”

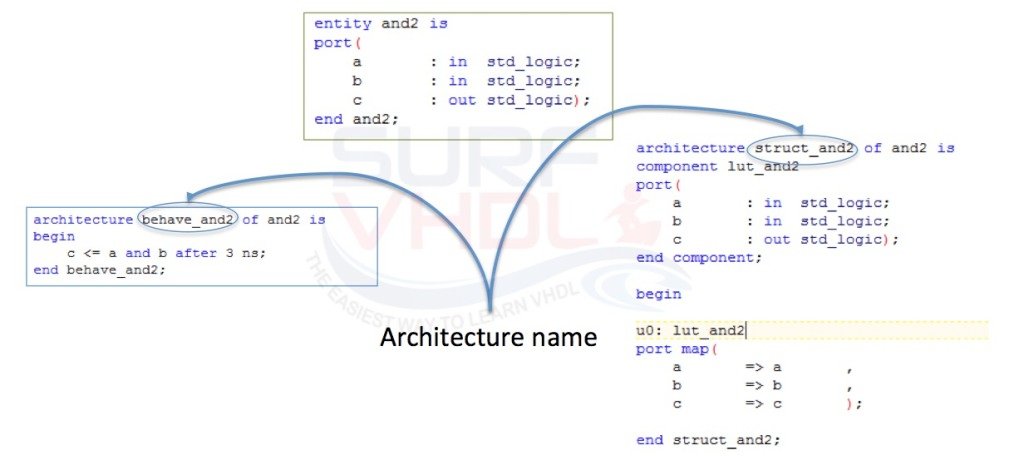

A single VHDL entity shall have at least one architecture. It is possible to have more than one architecture for the same entity.

For instance, and2 entity in this case have the “behave_and2” architecture in which is described the behavior of the entity and2 in a behavioral way.

In the architecture “behave_and2” the output c takes the value of a and b with a delay of 3 ns. Of course, this type of code cannot be implemented in hardware device. It is used only for test bench purpose. In fact the delay cannot be mapped in real hardware using the VHDL clause “after”. The delay is dependent only by hardware implementation of the logic and will be computed only after the layout. The static timing analysis will provide the report for internal logic delay.

In the other architecture “struct_and2”, it is present the instance of a component “lut_and2”. We are now introducing the concept of component instantiation. In this example, “lut_and2” is an and2 primitive component of the device.

VHDL Entity / Architecture golden rule:

I would like to show you few golden rules for entity / architecture pair implementation. Of course it is not mandatory to follow these simple rules, but they are a good design rules generally followed by hardware designer.

- Use only one architecture per entity : you can use more than one architecture per entity but doing this, the VHDL code implementation could be difficult to understand.

- Write the architecture description code in the same file where you write the VHDL entity definition.

- Use one VHDL file per entity / architecture pair.

- Use the same name for both entity and file: if the entity name is and2 then the file name should be and2.vhd