The Entity is the VHDL basic building block

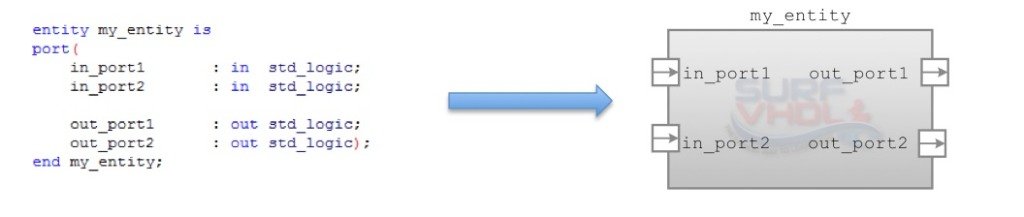

All the VHDL designs are implemented by entity. You can imagine the entity as a black box with input and output ports.

entity my_entity is port( in_port1 : in std_logic; in_port2 : in std_logic; out_port1 : out std_logic; out_port2 : out std_logic); end my_entity;

The BNF for VHDL entity is:

entity_declaration ::= entity identifier is entity_header entity_declarative_part [ begin entity_statement_part ] end [ entity_simple_name ] ; entity_header ::= [ formal_generic_clause ] [ formal_port_clause ] generic_clause ::= generic ( generic_list ) ; generic_list ::= generic_interface_list port_clause ::= port ( port_list ) ; port_list ::= port_interface_list entity_declarative_part ::= { entity_declarative_item }

All the VHDL designs are created with one or more entity. The entities allow you creating a hierarchy in the design.

An example is better than hundred explanations:

The entity syntax is keyword “entity”, followed by entity name and the keyword “is” and “port”.

Then inside parenthesis there is the ports declaration.

In the port declaration there are port name followed by colon, then port direction (in/out in this example) followed by port type. The entity declaration terminate with “end” keyword followed be entity name and semicolon.

VHDL entity declaration

VHDL Entity representing an “and gate” with two input ports a and b and output port c.

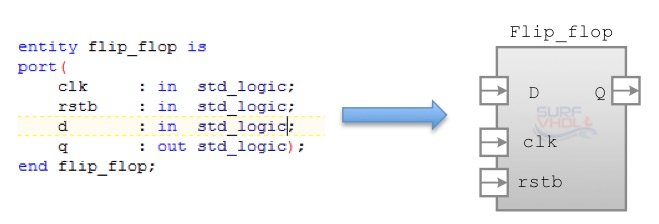

VHDL Entity representing a flip-flop type D with input port: clock and reset active low, data D, and output port Q.

VHDL Entity representing a multiplier with input operand a and b of 8 bit and output m of 16 bit.