In VHDL the designer has the possibility to perform a signal assignment after certain amount of time, implementing the delay in the assignment.

VHDL Delay Type

In VHDL there are two different kind of delay

- Transport delay

- Inertial delay

The transport delay is used to model the delay introduced by wire connection or a PCB connection.

The inertial delay models the delay introduced by an analog port, which means, it is analogous to the delay in devices that respond only if the signal value persists on their inputs for a given amount of time.

It is useful in order to ignore input glitches whose duration is less than the port delay.

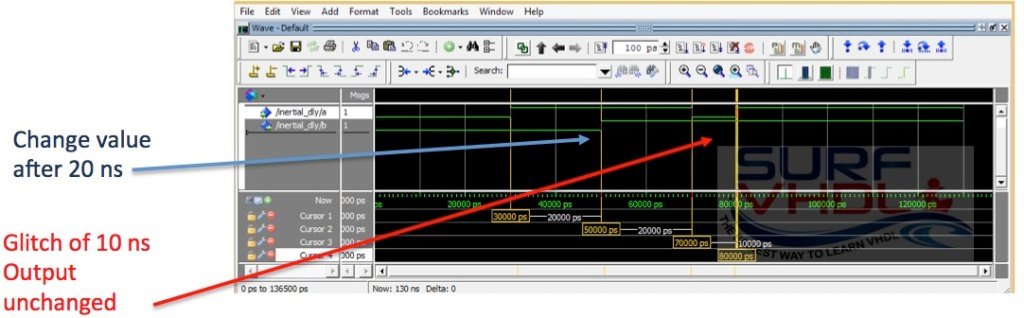

Inertial Delay Model

The inertial delay model is the default delay implemented in VHDL because it’s behavior is very similar to the delay of the device. The delay assignment syntax is:

b <= a after 20 ns;

In this example b take the value of a after 20 ns second of inertial delay.

This means that if a value varies faster than 20 ns b remain unchanged. This simulation should clarify the concept.

At simulation start a and b are 0; a change from 0 to 1, and b change its value after 20 ns;

then a changes value going to 0 and then to 1 in 10 ns.

This delay is less than inertial delay of 20 ns. So b remains unchanged.

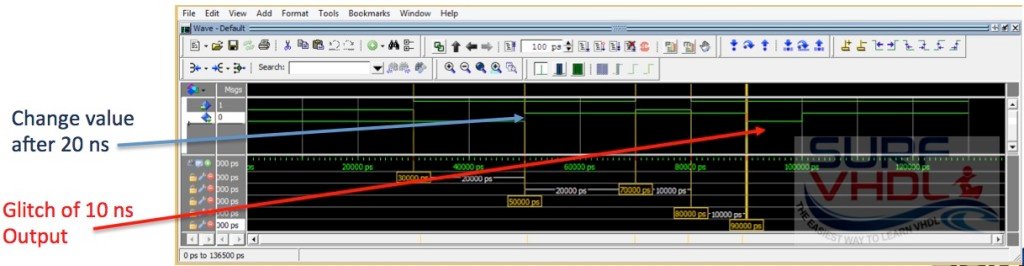

Transport Delay Model

The transport delay is not the default delay implemented in VHDL and must be specified. This delay model is useful to describe delay line, PCB delay, wire delay. The delay assignment syntax is:

b <= transport a after 20 ns;

in this example b take the value of a after 20 ns second of transport delay.

This means that no matter how fast a changes his value, b will follow the behavior of a after the amount of time specified in the delay statement . This simulation should clarify the concept.

The simulation is the same as the inertial delay. In this case the value of b follow the value of a after 20 ns even when a has a glitch of 10 ns

VHDL transport and inertial delay model allow the designer to model different type of behavior on VHDL hardware implementation. They are very useful in test bench modeling and in VHDL macro model delay modeling such as RAM, ROM, and peripheral interfacing.