VHDL allows the designer to parametrize the entity during the component instantiation.

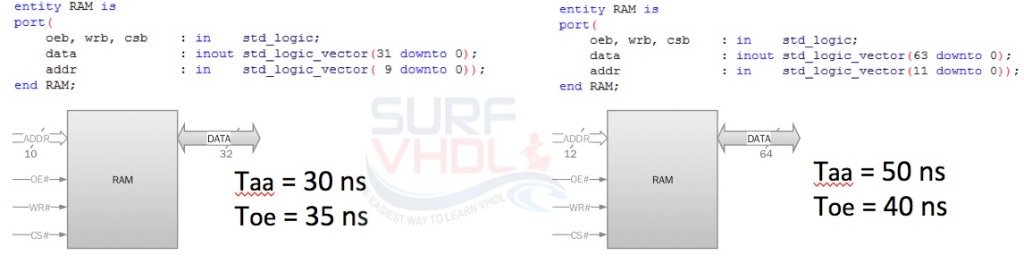

Imagine you need to write 2 RAM modules.

The RAMs are similar. Have the same interface in terms of signal but different access time address and BUS width. In this case, there is no need to write twice the same module. It should be possible to parameterize the component during the instantiation. In order to implement parameterization of an entity VHDL introduce the generic clause.

In the entity declaration, all the values that have to be customized can be passed using generic clause.

In the component instantiation, the generic map statement can map the new values in the component.

You should notice that in the entity declaration the generic parameters can have a default values.

entity RAM is generic( data_width : integer := 64; addr_width : integer := 12; Taa : time := 50; Toe : time := 40); port( oeb, wrb, csb : in std_logic; data : inout std_logic_vector(data_width-1 downto 0); addr : in std_logic_vector(addr_width-1 downto 0)); end RAM;

RAM1 : RAM generic map( data_width => 32, addr_width => 20, Taa => 30 ns, Toe => 35 ns) port map( oeb => oeb, wrb => wrb, csb => csb, data => data , addr => addr );

RAM2 : RAM

port map(

oeb => oeb, wrb => wrb, csb => csb,

data => data ,

addr => addr );

The default value is not mandatory. In this case (RAM2 instance) if no generic mapping is performed, the default values are applied in the current component instantiation.