The Conditional Signal Assignment statement is concurrent because it is assigned in the concurrent section of the architecture. It is possible to implement the same code in a sequential version, as we will see next.

The conditional signal assignment statement is a process that assigns values to a signal.

It is a concurrent statement; this means that you must use it only in concurrent code sections.

The statement that performs the same operation in a sequential environment is the “if” statement.

The syntax for a conditional signal assignment statement is:

a <= b when c=’1’ else d;

This is a simple example of a two-way mux as reported here:

The output “a” is equal to “b” when the selector “c” is “1” else is equal to “d”

Concurrent Conditional Signal Assignment Example 1

This example extends the previous one. This is a 4-way mux, implemented as concurrent code.

The architecture declarative section is empty. As you can notice, we don’t care about how the mux is implemented.

entity mux4 is

port(

a : in bit;

b : in bit;

c : in bit;

d : in bit;

s0 : in bit;

s1 : in bit;

e : out bit);

end mux4;

architecture mux4_a of mux4 is

-- declarative part: empty

begin

e <= a when (s1='0' and s0='0') else

b when (s1='0' and s0='1') else

c when (s1='1' and s0='0') else

d;

end mux4_a;

In this moment we don’t’ talk about logic gate, and or nand ect, we are describing the behavior of circuit using a high level description.

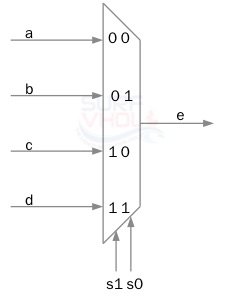

A graphical representation can be this one.

It is up to the synthesizer to implement the best architecture on the selected technology in terms of logic gates. In fact if you are using FPGA the synthesizer will use LUT to map the VHDL functions, if you are implementing an ASIC the synthesized logic will depend on differ technology and will be implemented using, for instance, NAND, OR, NOR gate, depending on the technology.

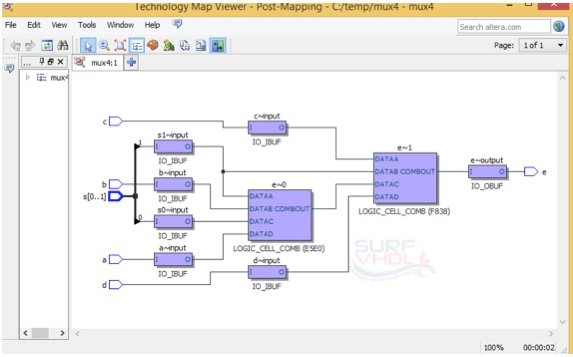

Running the RTL compiler on Altera Quartus II, this is the output of the RTL viewer, if we try to layout this mux4.

As clear, the RTL translation is implemented in terms of AND gate and 2-way mux. The output “e” is generated by cascading 3 two-way mux.

This is the output of the Altera MAP viewer selecting Cyclone IV FPGA technology. Our mux4 is implemented using LOGIC_COMB_CELL Look Up Table present in the Cyclone IV FPGA. This example should clarify the meaning of “technology dependent”.

Concurrent Conditional Signal Assignment Example 2

This example is the same 4-way mux as the previous one, in which we used a different syntax to implement the selector. In this case, we have introduced the statement “with select”.

entity mux4_select is

port(

a : in bit;

b : in bit;

c : in bit;

d : in bit;

s0 : in bit;

s1 : in bit;

e : out bit);

end mux4_select;

architecture mux4_select_a of mux4_select is

signal sel : integer;

begin

sel <= 0 when (s1='0' and s0='0') else

1 when (s1='0' and s0='1') else

2 when (s1='1' and s0='0') else

3;

with sel select

e <= a when 0,

b when 1,

c when 2,

d when others;

end mux4_select_a;

In the architecture declarative section, we declared a signal “sel” of type integer used to address the mux. The signal “sel” is coded as binary to integer.

The statement “with select” allows compacting the syntax of the mux code. Note the introduction of the “other” keyword. It is necessary because the mux assignment cover only 3 of the 2^32 possible integer values. If we try to layout the code, it is interesting to see how RTL viewer interprets the VHDL code:

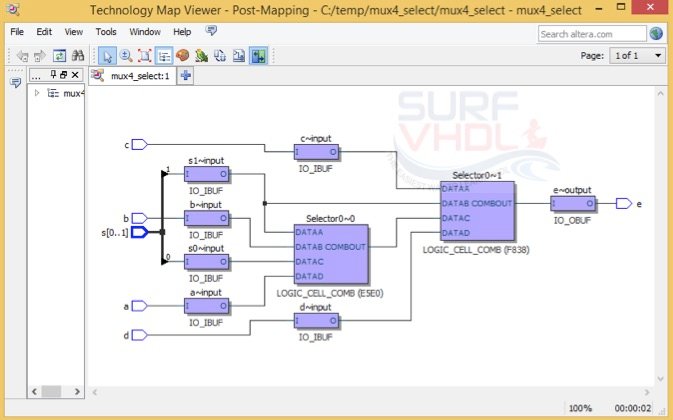

This case is different from the previous one. We can notice that the VHDL relative to the signal sel is decoded in order to implement mux selection and that the output mux is implemented as 4-way mux. So the RTL view of the RTL code is totally different from the previous one.

The FPGA used in this example is the same as the previous example, in fact the output of Altera MAP viewer have the same implementation of the previous RTL code as clear if we make a comparison between the two implementations.

These two examples should clarify the meaning of behavioral. We have seen two different implementations of a simple mux mapped on the same hardware:

implementation of different RTL code can generate the same hardware logic.

Of course, gaining the sensibility to write good VHDL/RTL code is only a matter of time and experience. If you will follow the course, you will find good advices in order to gain all the shortcuts useful reduce this amount of time.