VHDL multiple conditional statement

In this post, we have introduced the conditional statement. The IF-THEN-ELSE is a VHDL statement that allows implementing a choice between different options. When the number of options greater than two we can use the VHDL “ELSIF” clause. In case of multiple options, VHDL provides a more powerful statement both in the concurrent and sequential version:

- CASE-WHEN sequential statement

- WITH-SELECT concurrent statement

VHDL CASE and WITH-SELECT statement syntax

The BNF of the multiple VHDL conditional statement is reported below.

VHDL sequential CASE-WHEN statement BNF and example is:

case_statement ::=

case expression is

case_statement_alternative

{ case_statement_alternative }

end case ;

case_statement_alternative ::=

when choices =>

sequence_of_statements choices ::= choice { | choice }

choice ::= simple_expression

| discrete_range

| element_simple_name | others

EXAMPLE:

case element_colour of

when red => statements for red;

when green | blue => statements for green or blue;

when orange to turquoise => statements for these colours;

end case;

case opcode of

when X"00" => perform_add;

when X"01" => perform_subtract;

when others => signal_illegal_opcode;

end case;

VHDL concurrent WITH-SELECT statement BNF and example is:

with expression select

s <= waveform_1 when choice_list_1,

waveform_2 when choice_list_2,

...

waveform_n when choice_list_n;

with alu_function select

alu_result <= op1 + op2 when alu_add | alu_incr,

op1 – op2 when alu_subtract,

op1 and op2 when alu_and,

op1 or op2 when alu_or,

op1 and not op2 when alu_mask;

IF-THEN-ELSIF vs CASE statement

The considerations we are doing on the IF-THEN-ELSIF and CASE-WHEN sequential statement can be applied also to the concurrent version of the conditional statement. The sequential CASE-WHEN statement is more adopted in the common VHDL RTL coding for conditional statement with multiple options. It is more similar to the normal programming code approach even if the hardware implementation must be taken into account as parallel processing.

The IF-THEN-ELSIF statement implements a VHDL code that could be translated into a hardware implementation that performs priority on the choice selection. This came directly from the syntactic meaning of the IF-THEN-ELSIF statement.

When we use the CASE-WHEN statement no priority is implemented in the code and as consequence on the hardware instantiated.

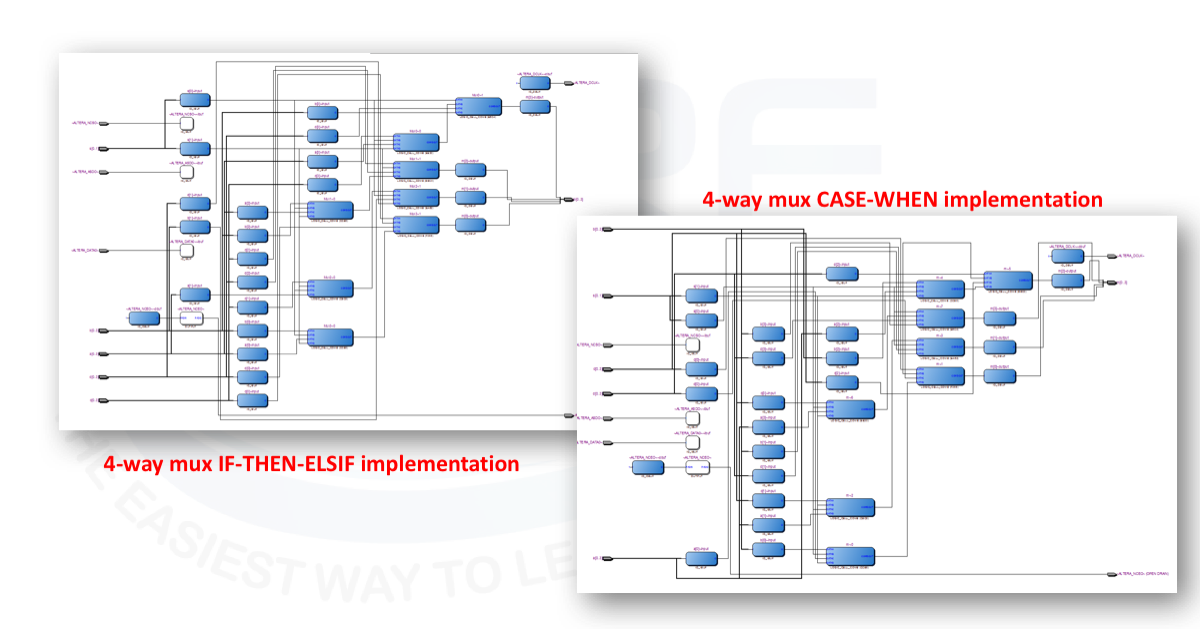

Here below we can see the same implementation of a 4-way mux using the IF-THEN-ELSIF and the CASE-WHEN statement.

library ieee ;

use ieee.std_logic_1164.all;

entity mux4_if is

port(

a : in std_logic_vector(3 downto 0);

b : in std_logic_vector(3 downto 0);

c : in std_logic_vector(3 downto 0);

d : in std_logic_vector(3 downto 0);

s : in std_logic_vector(1 downto 0);

m : out std_logic_vector(3 downto 0));

end mux4_if;

architecture rtl of mux4_if is

begin

p_mux : process(a,b,c,d,s)

begin

if (s = "00") then m <= a;

elsif(s = "01") then m <= b;

elsif(s = "10") then m <= c;

else m <= d;

end if;

end process p_mux;

end rtl;

VHDL code of 4-way mux using the sequential statement “if-then-elsif”

library ieee ;

use ieee.std_logic_1164.all;

entity mux4_case is

port(

a : in std_logic_vector(3 downto 0);

b : in std_logic_vector(3 downto 0);

c : in std_logic_vector(3 downto 0);

d : in std_logic_vector(3 downto 0);

s : in std_logic_vector(1 downto 0);

m : out std_logic_vector(3 downto 0));

end mux4_case;

architecture rtl of mux4_case is

begin

p_mux : process(a,b,c,d,s)

begin

case s is

when "00" => m <= a;

when "01" => m <= b;

when "10" => m <= c;

when others => m <= d;

end case;

end process p_mux;

end rtl;

VHDL code of 4-way mux using the sequential statement “case-when”

As clear from the RTL viewer in Figure2, the VHDL code of the 4-way mux is translated in two different VHDL-RTL implementations. In Figure2 on the left is reported the RTL view of the 4-way mux implemented using the IF-THEN-ELSIF VHDL coding style. A set of comparators are used to select the cascaded 2-way mux as described in the VHDL code. On the right is reported the straight forward 4-way mux implementation as described by the CASE-WHEN VHDL coding style.

Now we need a step forward. Looking at Figure 3 it is clear that the final hardware implementation is the same.

Different RTL views can be translated in the same hardware structure!

wait, wait… different RTL implementation can be translated in the same hardware circuit?

Yes!

As I always say to every guy that contact me,

you must think hardware!

Think about it: even if you are writing a VHDL code using IF-THEN-ELSIF statement, the final output comes from a 4-way mux. The logic synthesizer does its work simplifying the Boolean equations that come from your VHDL-RTL coding giving as result the 4-way mux we want to implement.

Conclusion

Every time we write a VHDL code to implement some hardware circuit, we need to pay attention to which VHDL instruction or construct is better to use.

As a rule of thumb, the selection of the RTL architecture is should be guided by the similarity of VHDL-RTL code to the final hardware.

A very good practice is also to verify the RTL viewer implementation and eventually, the final technology implementation both on the output reports and the technology viewer.

Reference

[1] RTL HARDWARE DESIGN USING VHDL Coding for Efficiency, Portability, and Scalability

[2] VHDL Programming by Example 4th Ed Douglas – Perry

[4] http://standards.ieee.org/findstds/standard/1076-1993.html

Thank you for your amazing lessons !

Thank you for your feedback!

ciao

Thank you for your wonderful education.

Thank you for your feedback!

I really appreciate it!

Good afternoon:

It is a very interesting paper, but The example commented corresponds to a Combinational logic, but you only analyzed two examples using the process command (sequential). So, I added another example using with-select-when command:

architecture rtl of mux4_case is

begin

with s select

m <=a when "00",

b when "01",

b when "10",

d when others;

end rtl;

I tried the three options in VIVADO and got the same implemented results but with LUT's, (different to the ones shown in your article), anyway confirming your statement.

Regards

Hi Ronald, thank you for your comment!