One of the major VHDL characteristics is the concurrency. In typical programming languages such as C++ or Visual Basic, the code is executed sequentially following the order of the statement in the source files.

Inside a VHDL architecture there is no specified order in the assignment statement. This means that if you exchange the order of two assignments the results is the same.

You may say: “why VHDL introduce such complication?”

You may think the VHDL is a hardware description language, this means that when you write a statements you are coding the implementation of a combinatorial or sequential logic.

If you keep in mind this concept, it will be clear that VHDL code is concurrent and not sequential as classical programming languages.

The order of execution is defined only by events occurring on the signals that the assignments are sensitive to.

Let’s try to make an example

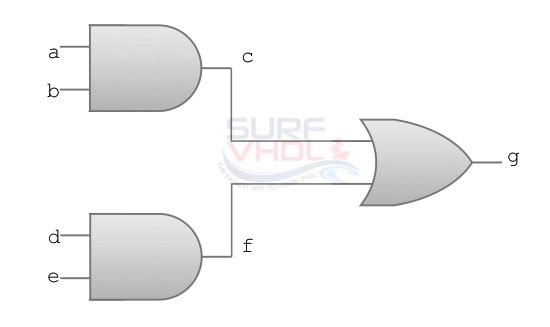

The VHDL entity “and_or” has 4 input ports and one output port.

A possible architecture implementation could be the follow:

entity and_or is port( a : in std_logic; b : in std_logic; d : in std_logic; e : in std_logic; g : out std_logic); end and_or; architecture and_or_a of and_or is signal c : std_logic; signal f : std_logic; begin c <= a and b; -- c assigment f <= d and e; -- f assigment g <= c or f; -- g assigment end and_or_a;

VHDL Concurrency Example 1

Where the assignment sequence is “c” than “f” than “g”.

It is clear that the same result will be evaluated from this implementation

architecture and_or_a of and_or is signal c : std_logic; signal f : std_logic; begin g <= c or f; -- g assigment f <= d and e; -- f assigment c <= a and b; -- c assigment end and_or_a;

VHDL Concurrency Example 2

Where the assignment are “g” than “f” than “c”.

It is clear that the output cannot be different. The only “solution” to have the same result is that allow the assignment statements evaluation concurrently. Every time you use VHDL you must remember that you are implementing hardware logic so you must

“Think hardware”

If you keep in mind this simple example, the concurrency in VHDL should be clear forever.