What is an array

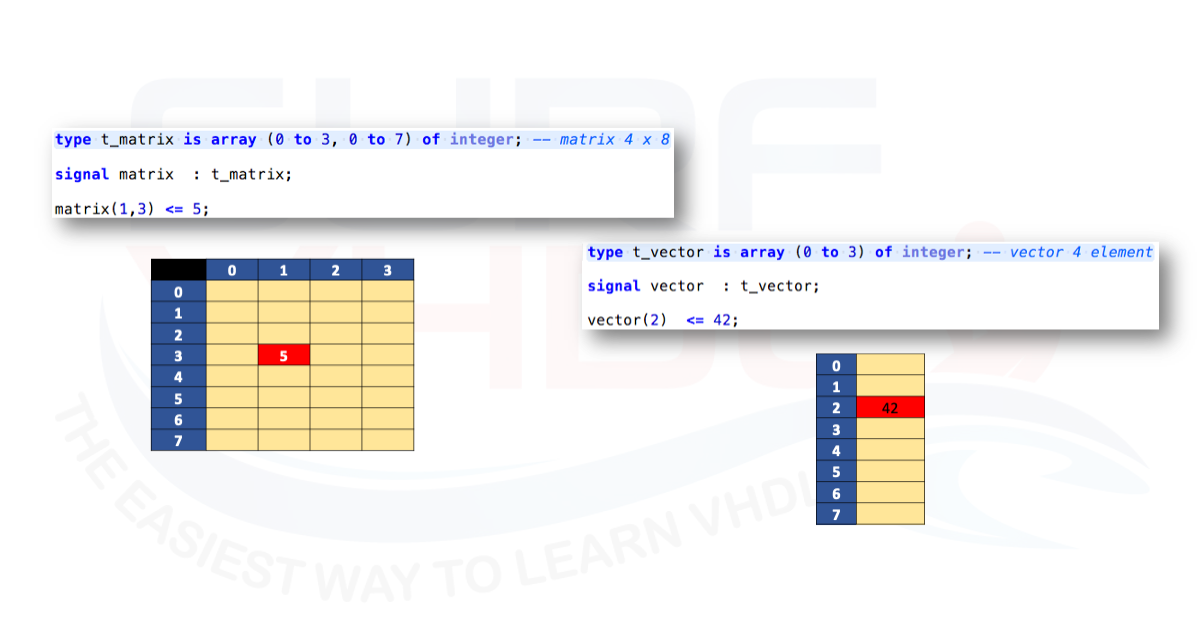

In any software programming language, when we need to deal with a collection of elements of the same type we can take advantage of the dedicated data structures provided by the language. In VHDL such kind of structure is defined “array“.

We can collect any data type object in an array type, many of the predefined VHDL data types are defined as an array of a basic data type.

An example is:

type string is array (positive range <>) of character; type bit_vector is array (natural range <>) of bit;